# **Linnæus University**

Sweden

Degree project

# Accelerated Deep Learning using Intel Xeon Phi

Author: André Viebke Supervisor: Sabri Pllana

External Supervisor: Narges Khakpour

Date: 2015-07-15

Course Code: 4DV01E, 15 credits

Level: Master

Department of Computer Science

#### **Abstract**

Deep learning, a sub-topic of machine learning inspired by biology, have achieved wide attention in the industry and research community recently. State-of-the-art applications in the area of computer vision and speech recognition (among others) are built using deep learning algorithms. In contrast to traditional algorithms, where the developer fully instructs the application what to do, deep learning algorithms instead learn from experience when performing a task. However, for the algorithm to learn require training, which is a high computational challenge. High Performance Computing can help ease the burden through parallelization, thereby reducing the training time; this is essential to fully utilize the algorithms in practice. Numerous work targeting GPUs have investigated ways to speed up the training, less attention have been paid to the Intel Xeon Phi coprocessor.

In this thesis we present a parallelized implementation of a Convolutional Neural Network (CNN), a deep learning architecture, and our proposed parallelization scheme, *CHAOS*. Additionally a theoretical analysis and a performance model discuss the algorithm in detail and allow for predictions if even more threads are available in the future. The algorithm is evaluated on an Intel Xeon Phi 7120p, Xeon E5-2695v2 2.4 GHz and Core i5 661 3.33 GHz using various architectures and thread counts on the MNIST dataset.

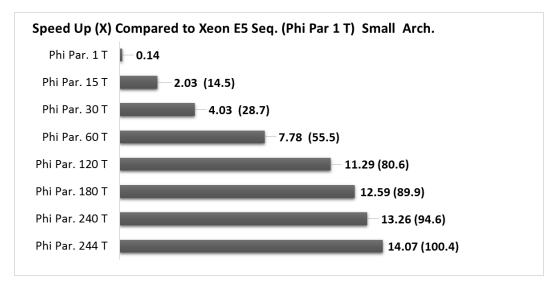

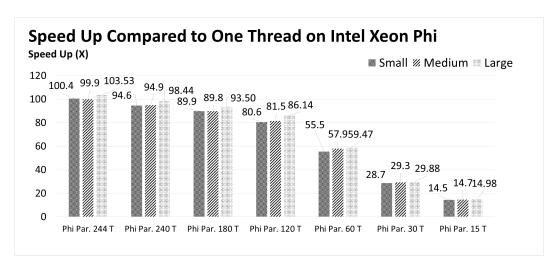

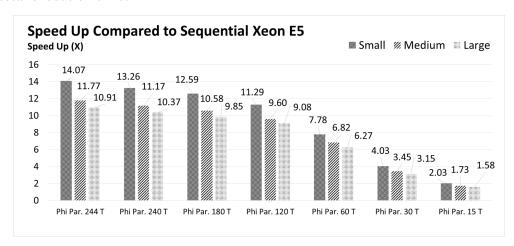

Findings show a **103.5x**, **99.9x**, **100.4x** speed up for the large, medium, and small architecture respectively for 244 threads compared to 1 thread on the coprocessor. Moreover, a **10.9x - 14.1x** (large to small) speed up compared to the sequential version running on Xeon E5. We managed to decrease training time from *7 days* on the Core i5 and *31 hours* on the Xeon E5, to *3 hours* on the Intel Xeon Phi when training our large network for 15 epochs.

#### Sammanfattning

deep learning, ett delämne inom maskininlärning, har på den senaste tiden fått stor uppmärksamhet både i näringslivet och forskarsamhället. State-of-the-art applikationer inom computer vision och speech recognition är byggda på deep learning algoritmer. I jämförelse med traditionella algoritmer där utvecklaren instruerar vad som ska utföras i detalj, lär sig deep learning algoritmer genom erfarenhet att uträtta uppgiften som den ska bli bra på. Hursomhelst, för att algoritmen ska kunna lära sig krävs mycket träning vilket är en stor beräkningsbörda. High Performance Computing kan minska bördan genom att parallellisera träningen och därmed minska träningstiden; vilket är vitalt för att kunna använda tekniken fullt ut i praktiken. Flertalet arbeten undersöker potentialen av grafikprocessorer (GPU), men få har undersökt Intel Xeon Phi.

I denna tes presenterar vi en parallell implementation av *Convolutional Neural Network* (*CNN*), en *deep learning* arkitektur, och vår förslagna paralleliseringsschema, *CHAOS*. Därutöver presenteras en teoretisk analys och en *performance model* som tillåter diskutera algoritmen och grovt uppskatta exekveringstiden om fler trådar skulle bli tillgängliga i framtiden. Algoritmen utvärderas på Intel Xeon Phi 7120p, Xeon E5-2695v2 2.4 GHz och Core i5 661 3.33 GHz genom olika arkitekturer och antal trådar på datamängden MNIST.

Resultaten påvisar en **103.5x**, **99.9x**, **100.4x** *speed up* för stor, mellan och liten arkitektur respektive, för 244 trådar jämfört med 1 tråd på Xeon Phi. Dessutom **10.9x - 14.1x** (stor till liten) *speed up* i jämförelse med den sekventiella versionen på Xeon E5. Vi lyckades minska träningstiden från *7 dagar* på Intel Core i5 till *31 timmar* på Xeon E5, och *3 timmar* på Intel Xeon Phi när vi tränade vårt stora nätverk 15 epoker.

**Keywords:** Machine Learning, Deep Learning, Supervised Deep Learning, Intel Xeon Phi, Convolutional Neural Network, CNN, High Performance Computing, CHAOS, parallel computing, coprocessor, MIC, speed up, performance model, evaluation

#### **Preface**

First of all I would like to express my thankfulness for the opportunity to perform this project. I would like to share my gratitude with my supervisor, Sabri, who helped guide me throughout the project. I also want to thank my future wife for enduring the late evenings and weekends I spent on this project.

Both deep learning and Intel Xeon Phi were topics completely new to me before initiating this study. It is now afterwards I recognize what I have missed out by not study them earlier. I am convinced that deep learning algorithms will drive the future of applications. As these applications require computational resources, there is no doubt such algorithms need to be parallelized or otherwise make use of high computational platforms to meet their computational needs.

We began this project with a wondering: how can Intel Xeon Phi facilitate deep learning Algorithms? Although several papers have been published during the last couple of years targeting GPUs, few have been published for the Intel Xeon Phi. This wondering is what initiated, and drove this study.

#### Förord

Först och främst vill jag framföra min tacksamhet för att ha fått möjlighet att utföra detta projekt. Jag vill tacka min handledare Sabri, som vägledde mig genom projektet. Jag vill också tacka min framtida fru för att stått ut med långa kvällar och helger som spenderats på projektet.

Både *deep learning* och *Intel Xeon Phi* var ämnen helt nya för mig innan jag påbörjade arbetet. Det är först nu efteråt som jag förstår vad jag missat genom att inte studera dem tidigare. Jag är övertygad om att *deep learning* kommer att vara en del av framtidens applikationer. Eftersom dessa kräver mycket beräkningskraft råder det inget tvivel om att dessa behöver parallelliseras eller på något sätt använda sig av plattformar med hög beräkningskapacitet som möter deras behov.

Vi började projektet med en undran: hur kan *Intel Xeon Phi* underlätta *deep earning* algoritmer? Mycket material har publicerats relaterade till grafikprocessorer (GPU) men väldigt få för *Intel Xeon Phi*. Denna undran initierade, och drev vår studie.

### **Publications**

A. Viebke and S. Pllana, "The potential of the Intel Xeon Phi for supervised Deep Learning," in IEEE HPCCC 2015. New York: IEEE, 2015.

# **Contents**

| 1 | Intr | oductio |                                                                    |

|---|------|---------|--------------------------------------------------------------------|

|   | 1.1  | Deep I  | Learning and the Intel Xeon Phi                                    |

|   | 1.2  | Relate  | d Work                                                             |

|   |      | 1.2.1   | Datasets in Related Work                                           |

|   |      | 1.2.2   | Applications of Intel Xeon Phi                                     |

|   |      | 1.2.3   | Related Work Targeting CNNs 6                                      |

|   |      | 1.2.4   | Example of Implementations and Libraries                           |

|   | 1.3  | Outlin  | e                                                                  |

| 2 | Bacl | kground | d 9                                                                |

| _ | 2.1  |         | Geon Phi                                                           |

|   | 2.2  |         | and CNNs                                                           |

|   | 2.2  | 2.2.1   | DNN Architecture                                                   |

|   |      | 2.2.2   | Forward Propagation                                                |

|   |      | 2.2.3   | Back-propagation                                                   |

|   |      | 2.2.4   | Overfitting, Dropout and Early Stopping                            |

|   |      | 2.2.5   | CNNs                                                               |

|   | 2.3  |         | Geon Phi Optimization Techniques                                   |

|   |      | 2.3.1   | Algorithmic Optimization Techniques                                |

|   |      | 2.3.2   | Micro Architectural Optimization Techniques                        |

|   | 2.4  |         | elization Schemes for Stochastic Gradient Descent                  |

|   |      | 2.4.1   | Model- and Data-Parallelism                                        |

|   |      | 2.4.2   | Strategy A: Hybrid                                                 |

|   |      | 2.4.3   | Strategy B: Averaged Stochastic Gradient                           |

|   |      | 2.4.4   | Strategy C: Delayed Stochastic Gradient                            |

|   |      | 2.4.5   | Strategy D: HogWild!                                               |

|   |      | 2.4.6   | Model Parallelism                                                  |

| 3 | The  | Approa  | ach 21                                                             |

| • | 3.1  |         | on of Implementation                                               |

|   | 3.2  |         | S: Controlled HogWild with Arbitrary Order of Synchronization . 22 |

|   | 3.3  |         | mentation                                                          |

|   | 0.0  | 3.3.1   | Sequential Implementation                                          |

|   |      | 3.3.2   | Parallel Implementation                                            |

|   | 3.4  |         | ation Approach                                                     |

|   | 3.5  |         | sis Approach                                                       |

| 4 | Resi | ulte    | 34                                                                 |

| • | 4.1  |         | tion Time, Speed Up and Prediction Accuracy                        |

|   | 7.1  |         | Results on the Small CNN Architecture                              |

|   |      | 7.1.1   |                                                                    |

|        | <i>5</i> 2         | 5.2.3 Speed Up of the Algorithm                                                                                        | 57<br>58 |  |  |  |  |

|--------|--------------------|------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

|        | 5.3<br>5.4         | CNN Architectures                                                                                                      | 58<br>59 |  |  |  |  |

|        | 3.4                | 5.4.1 Design of the Performance Model                                                                                  | 59<br>62 |  |  |  |  |

| 6      | Results Analysis 6 |                                                                                                                        |          |  |  |  |  |

|        | 6.1                | Experimental Analysis                                                                                                  | 66       |  |  |  |  |

|        |                    | 6.1.1 Execution Time and Speed Up                                                                                      | 67       |  |  |  |  |

|        |                    | 6.1.2 Time Spent at Each Layer                                                                                         | 69<br>70 |  |  |  |  |

|        | 6.2                | 6.1.3 Prediction Accuracy                                                                                              | 70<br>72 |  |  |  |  |

|        | 6.3                | RQ1: What is the Potential of Intel Xeon Phi for Supervised Deep Learn-                                                | 12       |  |  |  |  |

|        |                    | ing Algorithms?                                                                                                        | 73       |  |  |  |  |

| 7      | Disc               | eussion                                                                                                                | 75       |  |  |  |  |

|        | 7.1                | Social Impact and Ethical Considerations                                                                               | 75       |  |  |  |  |

|        | 7.2                | Reliability and Validity of the Results                                                                                | 75       |  |  |  |  |

|        | 7.3                | Contributions                                                                                                          | 76       |  |  |  |  |

|        | 7.4                | Personal Reflections on the Method                                                                                     | 77       |  |  |  |  |

|        |                    | 7.4.1 Personal Reflections on the Selection of Implementation 7.4.2 Personal Reflections on the Parallelization Scheme | 77       |  |  |  |  |

|        |                    | <ul><li>7.4.2 Personal Reflections on the Parallelization Scheme</li></ul>                                             | 77<br>78 |  |  |  |  |

|        | 7.5                | Limitations of the Study                                                                                               | 78       |  |  |  |  |

|        | 7.6                | Conclusion                                                                                                             | 79       |  |  |  |  |

|        | 7.7                | Future Work                                                                                                            | 79       |  |  |  |  |

| A      | Plat               | forms                                                                                                                  | 1        |  |  |  |  |

| В      | Deta               | ails of CNN Architectures                                                                                              | 2        |  |  |  |  |

| C      | Vect               | torization Reports                                                                                                     | 5        |  |  |  |  |

| $\sim$ |                    | <b>1</b>                                                                                                               |          |  |  |  |  |

| D      | Evo                | cution and Validation Details                                                                                          | 7        |  |  |  |  |

|   | D.2 | Standard Deviation of the Results                         | 7  |

|---|-----|-----------------------------------------------------------|----|

|   | D.3 | Execution Reports for the Experiments                     | 9  |

| E | Add | itional Theoretical Analysis                              | 11 |

|   | E.1 | Forward Propagate Function for the Max Pooling Layers     | 11 |

|   | E.2 | Forward Propagate Function for the Fully Connected Layers | 12 |

|   | E.3 | Forward Propagate Function for the Convolutional Layers   | 13 |

|   | E.4 | Back-propagate Function for the Max Pooling Layers        | 14 |

|   | E.5 | Back-propagate Function for the Fully Connected Layers    | 14 |

|   | E.6 | Back-propagate Function for the Convolutional Layers      | 15 |

|   | E.7 | Determine Error For Chunk Function                        | 17 |

|   | E.8 | Other Functions                                           | 17 |

| F | Add | itional Results                                           | 19 |

|   | F.1 | Results for Intel Xeon E5                                 | 19 |

|   | F.2 | Speed Up compared to Intel Core i5                        | 20 |

# **List of Figures**

| 1.1.1  | A DNN                                                                       | 2  |

|--------|-----------------------------------------------------------------------------|----|

| 2.1.1  | The architecture of Intel Xeon Phi                                          | 10 |

| 2.2.1  | A deep neural network                                                       | 12 |

| 2.2.2  | A CNN with 5 layers emphasizing the kernels. Courtesy to Dan Cireşan        |    |

|        | et al [1]                                                                   | 14 |

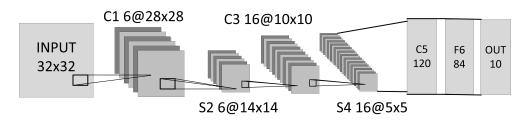

| 2.2.3  | The traditional LeNet-5 architecture [2]                                    | 15 |

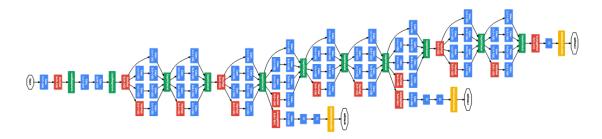

| 2.2.4  | GoogleNet [3]                                                               | 15 |

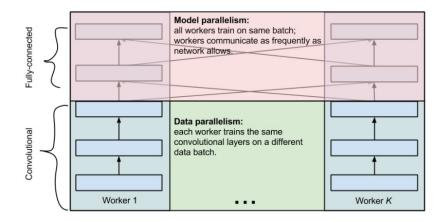

| 2.4.1  | The hybrid approach of data- and model-parallelism. Courtesy to Alex        |    |

|        | Krizhevsky [4]                                                              | 19 |

| 3.1.1  | Extract from MNIST dataset. Courtesy to Y. Tang et al. [5]                  | 22 |

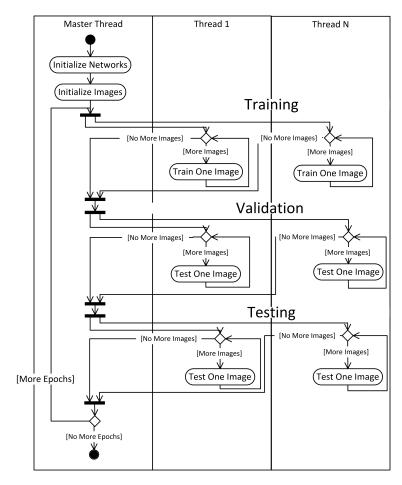

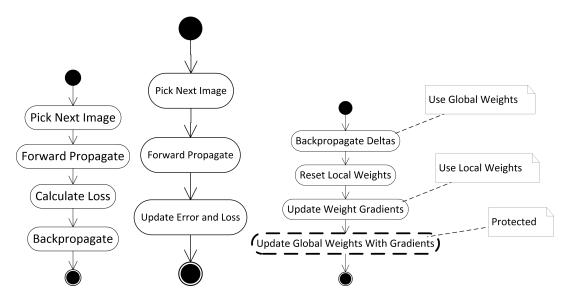

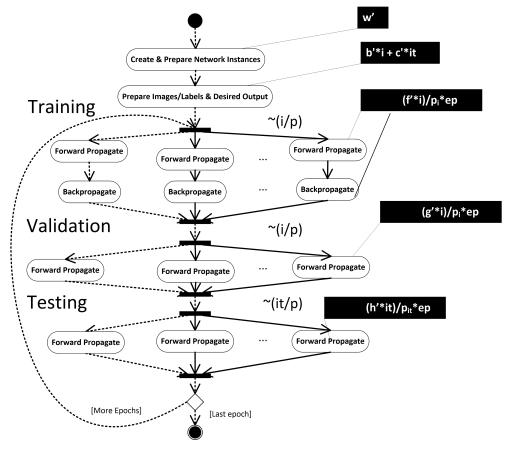

| 3.2.1  | Activity diagram of CHAOS.                                                  | 24 |

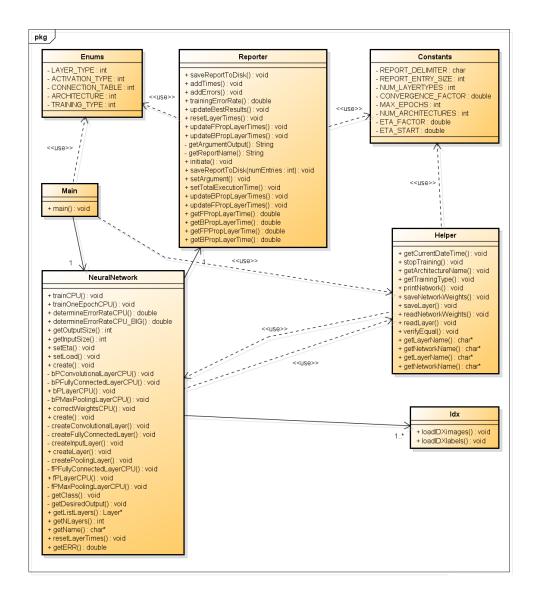

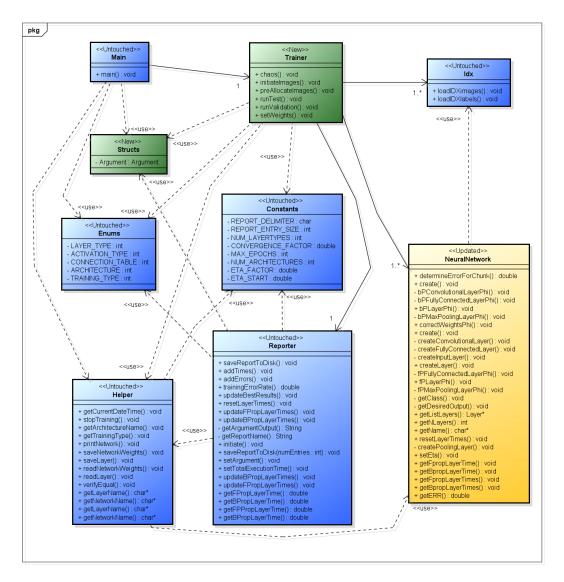

| 3.3.1  | Class diagram for the sequential version.                                   | 26 |

| 3.3.2  | The training (left), testing (center), and back-propagation (right) of one  | 20 |

| 3.3.2  | image                                                                       | 27 |

| 3.3.3  | Class diagram for the parallel implementation                               | 28 |

| 0.0.0  |                                                                             |    |

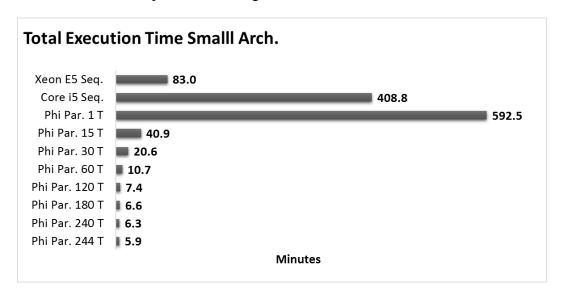

| 4.1.1  | Total execution time for the small CNN architecture                         | 35 |

| 4.1.2  | Speed up for the small CNN architecture compared to <i>Xeon E5 Seq (Phi</i> |    |

|        | <i>Par. 1 T</i> )                                                           | 35 |

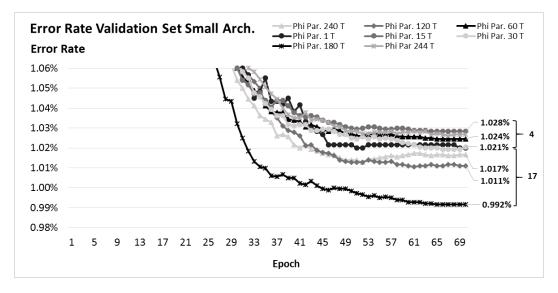

| 4.1.3  | Error rate of the validation set for the small CNN architecture             | 36 |

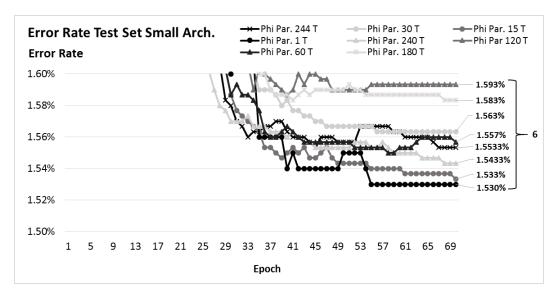

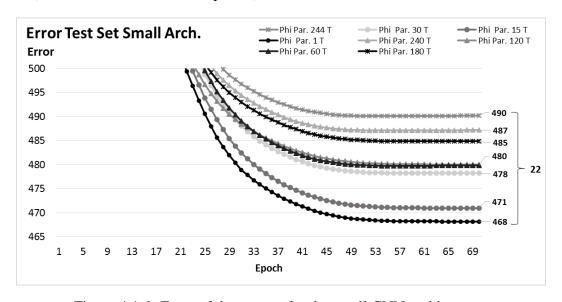

| 4.1.4  | Error rate of the test set for the small CNN architecture                   | 36 |

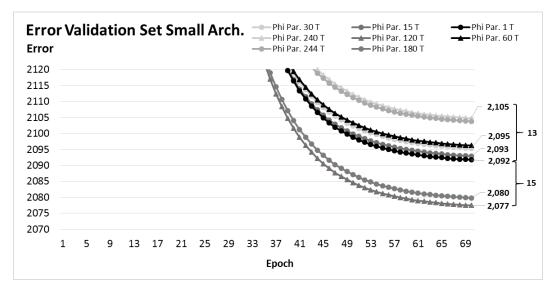

| 4.1.5  | Error of the validation set for the small CNN architecture                  | 37 |

| 4.1.6  | Error of the test set for the small CNN architecture                        | 37 |

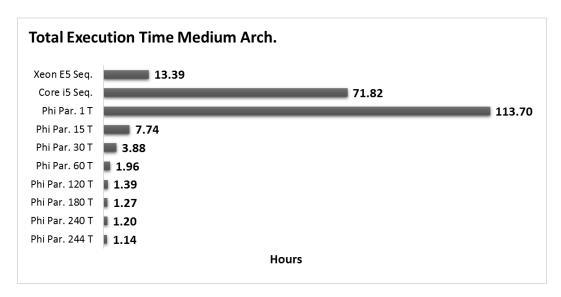

| 4.1.7  | The total execution time for the medium CNN architecture                    | 38 |

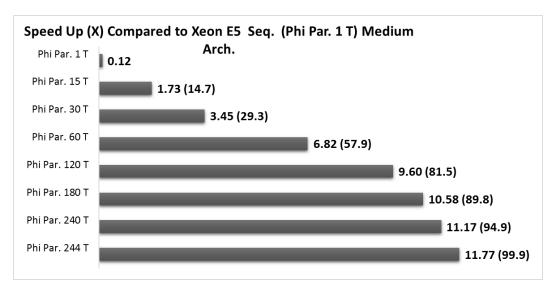

| 4.1.8  | The speed up for the medium CNN architecture compared to <i>Xeon E5</i>     |    |

|        | Seq (Phi Par. 1 T)                                                          | 38 |

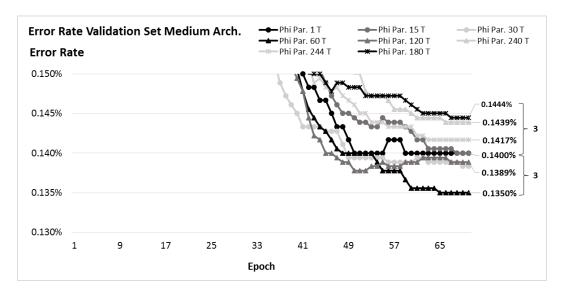

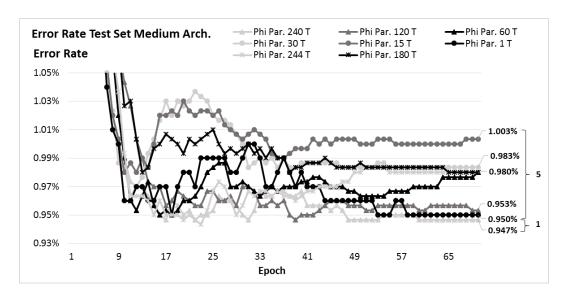

| 4.1.9  | Error rate of the validation set for the medium CNN architecture            | 39 |

|        | Error rate of the test set for the medium CNN architecture                  | 39 |

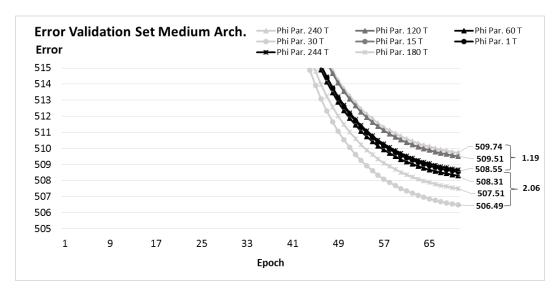

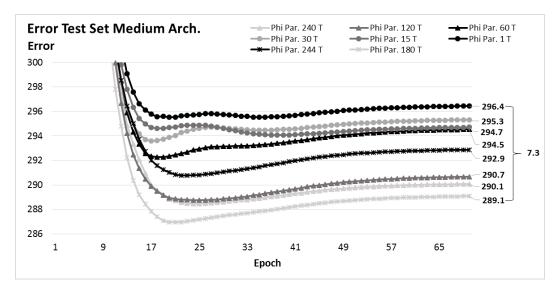

|        | Error of the validation set for the medium CNN architecture                 | 40 |

|        | Error of the test set for the medium CNN architecture                       | 40 |

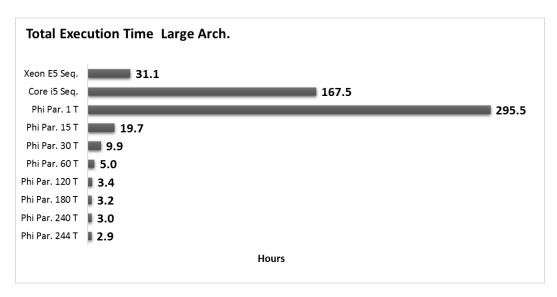

|        | Total execution time for the large CNN architecture                         | 41 |

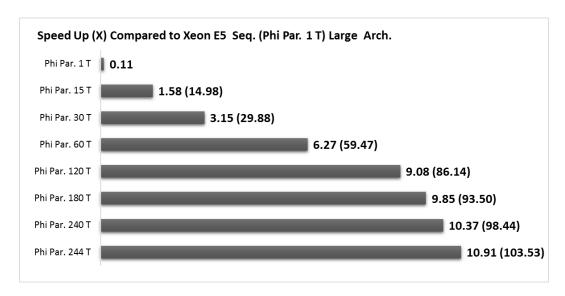

| 4.1.14 | Speed up for the large CNN architecture as compared to <i>Xeon E5 Seq</i>   |    |

|        | (Phi Par. 1 T)                                                              | 41 |

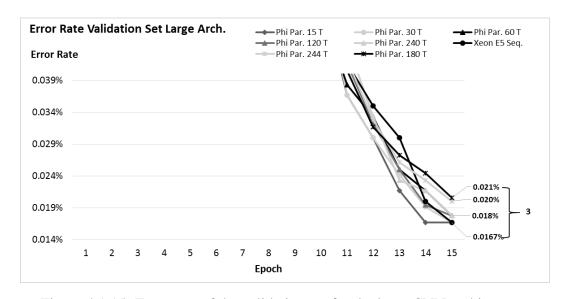

|        | Error rate of the validation set for the large CNN architecture             | 42 |

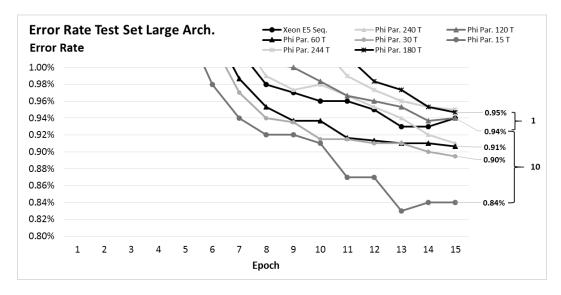

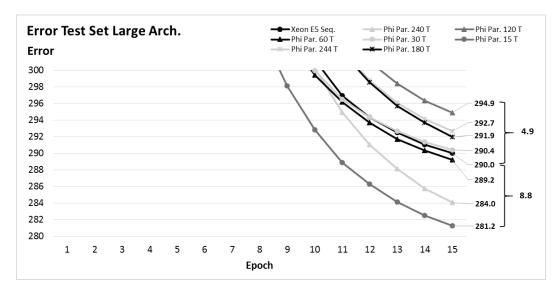

|        | Error rate of the test set for the large CNN architecture                   | 42 |

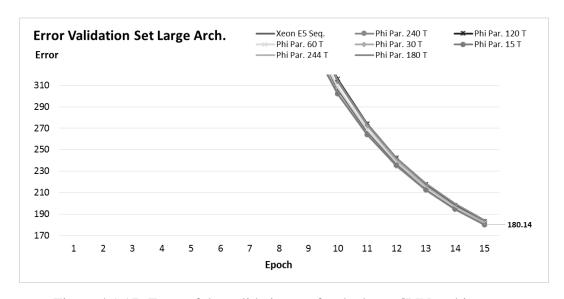

|        | Error of the validation set for the large CNN architecture                  | 43 |

| 4.1.18 | Error of the test set for the large CNN architecture                        | 43 |

| 5.2.1  | An overview of <i>CHAOS</i>                                                 | 56 |

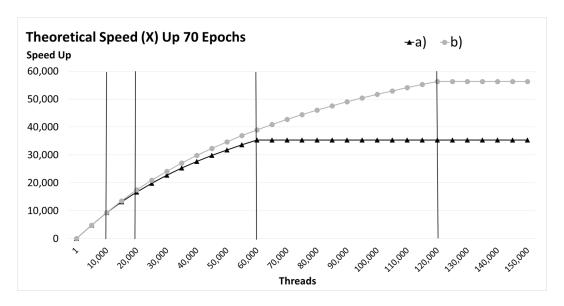

| 5.2.2  | Instantiation of the theoretical speed up model                             | 58 |

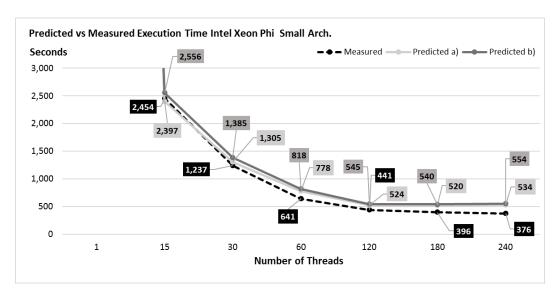

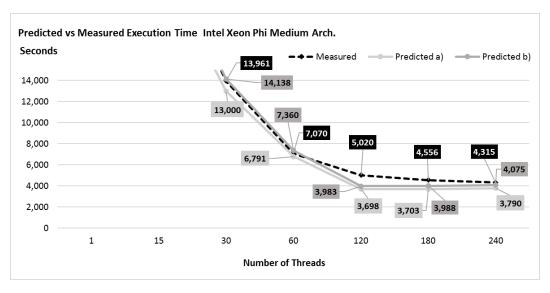

| 5.4.1 | Predicted vs Measured execution times for Intel Xeon Phi using the small CNN architecture      | 63 |

|-------|------------------------------------------------------------------------------------------------|----|

| 5.4.2 | Predicted vs Measured execution times for the Intel Xeon Phi using the medium CNN architecture | 63 |

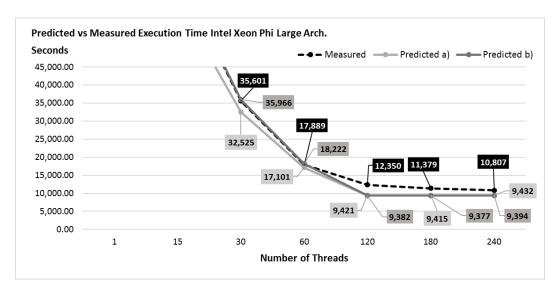

| 5.4.3 | Predicted vs Measured execution times for Intel Xeon Phi using the                             |    |

|       | large CNN architecture                                                                         | 64 |

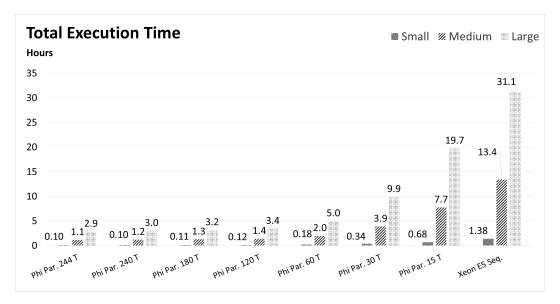

| 6.1.1 | Total execution times for all CNN architectures on the Xeon Phi, and                           |    |

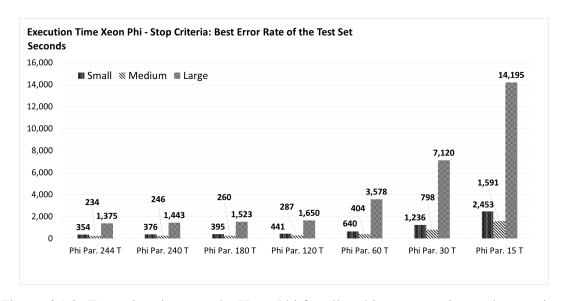

|       | <i>Xeon E5 Seq.</i>                                                                            | 68 |

| 6.1.2 | Execution times on the Xeon Phi for all architectures, using early stopping.                   | 68 |

| 6.1.3 | Speed up compared to <i>Phi Par. 1 T</i> for all architectures                                 | 69 |

| 6.1.4 | Speed up compared to Xeon E5 Seq for all CNN architectures when                                |    |

|       | executed on the Xeon Phi                                                                       | 69 |

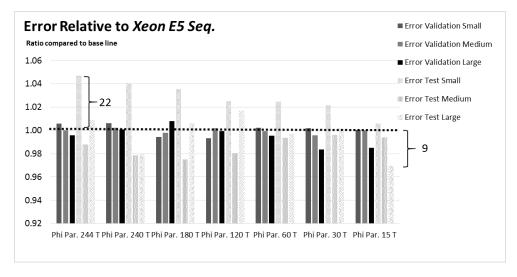

| 6.1.5 | Relative cumulative error (loss) compared to <i>Xeon E5 Seq.</i>                               | 70 |

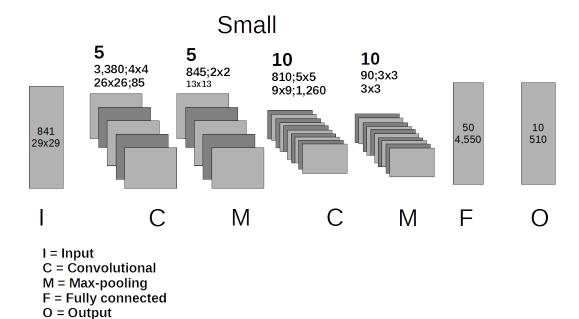

| B.0.1 | Details of the small CNN architecture                                                          | 2  |

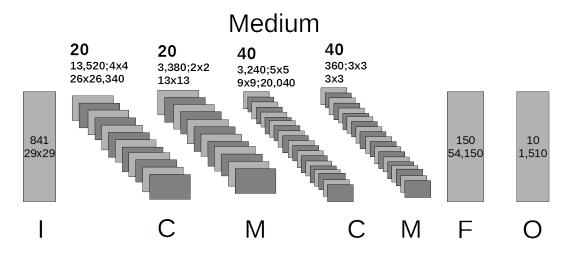

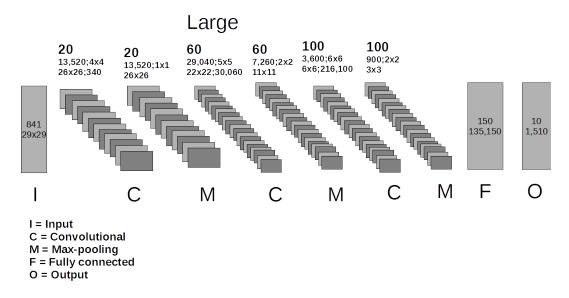

| B.0.2 | Details of the medium CNN architecture                                                         | 3  |

| B.0.3 | Details of the large CNN architecture                                                          | 3  |

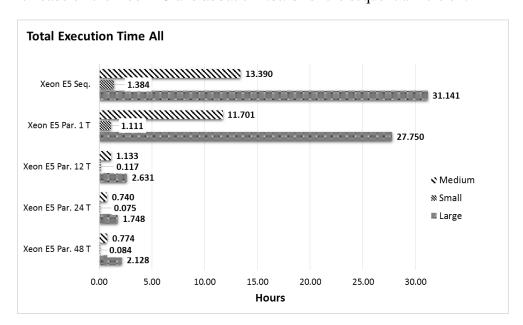

| F.1.1 | The total execution time for all CNN architectures on the Xeon E5, for                         |    |

|       | various thread counts                                                                          | 19 |

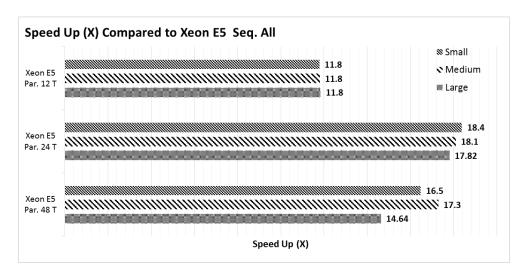

| F.1.2 | Speed up compared to Xeon E5 Seq. for all architectures and thread                             |    |

|       | counts on the Xeon E5                                                                          | 20 |

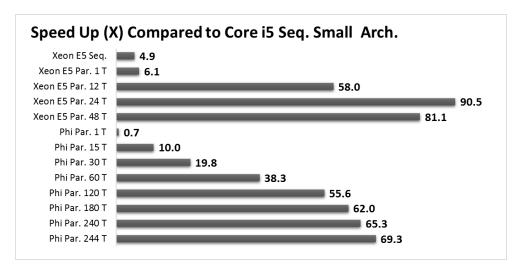

| F.2.1 | Speed up compared to <i>Core i5 Seq.</i> for the small architecture                            | 20 |

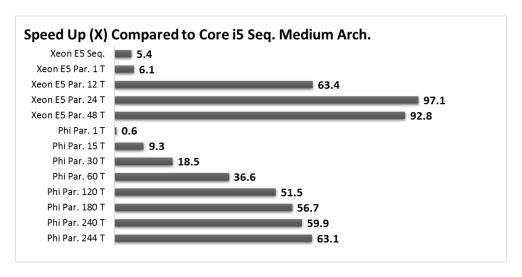

| F.2.2 | Speed up compared to <i>Core i5 Seq.</i> for the medium architecture                           | 21 |

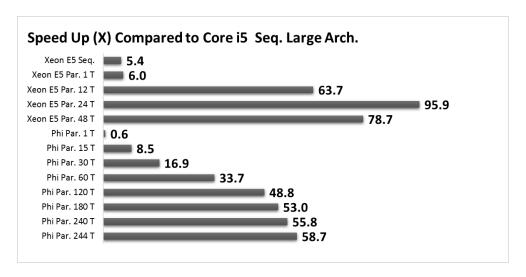

| F.2.3 | Speed up compared to <i>Core i5 Sea</i> , for the large architecture                           | 21 |

# **List of Tables**

| 1.2.1 | Some useful implementations and libraries for deep learning and CNNs.                                    | 8        |

|-------|----------------------------------------------------------------------------------------------------------|----------|

| 3.3.1 | Execution times at each layer for the sequential version on the Xeon E5 using the small CNN architecture | 27       |

| 3.4.1 | Planned execution scheme                                                                                 | 31       |

| 3.4.2 | CNN architectures used in evaluation                                                                     | 32       |

| 4.2.1 | Average layer times for the small CNN architecture                                                       | 44       |

| 4.2.2 | Average layer times for the medium CNN architecture                                                      | 44       |

| 4.2.3 | Average layer times for the large CNN architecture                                                       | 45       |

| 5.1.1 | Parameters used in the theoretical analysis                                                              | 47       |

| 5.3.1 | Number of operations when forward propagating one image for different CNN architectures                  | 59       |

| 5.3.2 | The number of operations when back-propagating one image for differ-                                     |          |

|       | ent CNN architectures                                                                                    | 59       |

| 5.4.1 | Variables used in the performance model                                                                  | 60       |

| 5.4.2 | Hardware independent parameters used in the performance model                                            | 60       |

| 5.4.3 | Hardware specific parameters used in the performance model                                               | 61       |

| 5.4.4 | Measured and predicted memory contention (s) for the Intel Xeon Phi                                      | 61       |

| 5.4.5 | Averaged deviation in predictions for both prediction models and all considered CNN architectures        | 64       |

| 5.4.6 | Predicted execution times (min) for 480, 960, 1,920 and 3,840 images                                     |          |

| 5.4.7 | using the performance models                                                                             | 65<br>65 |

|       |                                                                                                          |          |

| 6.1.1 | CNN architectures used in evaluation                                                                     | 67       |

| 6.1.2 | Averaged layer speed up compared to the <i>Phi Par. 1 T.</i>                                             | 70       |

| 6.1.3 | The number of incorrectly predicted images for the different CNN architectures                           | 71       |

| D.2.1 | Average standard deviation for the error, error rates and execution time                                 |          |

|       | for the small CNN architecture                                                                           | 8        |

| D.2.2 | Average standard deviation for the error, error rates and execution time for the medium CNN architecture | 8        |

| D 2 2 |                                                                                                          | 0        |

| D.2.3 | Average standard deviation for the error, error rates and execution time for the large CNN architecture  | 9        |

| D.3.1 | Execution report for the small architecture                                                              | 9        |

| D.3.2 | Execution report for the medium architecture                                                             | 10       |

| D.3.3 | Execution report for the large architecture                                                              | 10       |

| E.0.1 | Abbreviations used in the theoretical analysis                                                           | 11       |

| F.1.1 | The ending error and error rates for the Xeon E5 on all CNN architec- |    |

|-------|-----------------------------------------------------------------------|----|

|       | tures compared to the base line $Seq$                                 | 20 |

# Listings

| 3.1         | Code snippet for the update of weight parameters                        | 29 |

|-------------|-------------------------------------------------------------------------|----|

| 3.2         | Vectorization report for forward propagation in the convolutional layer | 29 |

| 5.1         | Listings of the main function                                           | 48 |

| 5.2         | Pseudocode for the trainer                                              | 49 |

| 5.3         | Pseudocode for the forwardPropagate function                            | 51 |

| 5.4         | Pseudocode for the backPropagate function                               | 52 |

| 5.5         | Pseudocode for the runTest function                                     | 53 |

| <b>C</b> .1 | Vectorization report for forward propagation in the convolutional layer | 5  |

| C.2         | Vectorization report for back-propagation in the fully connected layer  | 5  |

| C.3         | Vectorization report for back-propagation in the convolutional layer    | 6  |

| E.1         | Pseudocode for forward propagation in the max-pooling layer             | 12 |

| E.2         | Pseudocode for forward propagation in the fully connected layer         | 12 |

| E.3         | Pseudocode for forward propagation in the convolutional layer           | 13 |

| E.4         | Pseudocode for back-propagation in the max-pooling layer                | 14 |

| E.5         | Pseudocode for back-propagation in the fully connected layer            | 14 |

| E.6         | Pseudocode for back-propagation in the convolutional layer              | 15 |

| E.7         | Pseudocode for the determineErrorForChunk function                      | 17 |

#### **Glossary**

A short glossary with terms used in the study.

- Machine learning A group of algorithms learning from experience in performing a task.

- **Deep neural network (DNN)** Non-linear, complex, hierarchic models inspired by biology solving complex problems in computer science.

- Convolutional Neural Network (CNN) A specific type of DNNs introducing convolutional and pooling layers inspired the behaviour of the visual cortex of animals.

- **High Performance Computing (HPC)** The use of parallel processing power beyond the TFLOPS boundary facilitating high computational loads.

- **Intel Xeon Phi** A HPC device from Intel with up to 61 cores (Knights Corner) and in total 244 threads performing 1.2 TFLOPS.

- **VPU** Vector Processing Unit is a part of modern processing units allowing several scalar operations to be merged into vector operations and thus lower the number of instructions (and cycles) required.

- **OpenMP** An API/library facilitating the use of thread-, and data-parallelism by using pragmas and library routines, removing the necessity for developers to manage threading and SIMD instructions manually.

- **Speed Up** The fraction of how much faster the parallel version is compared to a base lined version.

- Data- and model-parallelism Two concepts used in parallelization of CNNs to define how the problem is divided over threads in the host system. Data-parallelism denote that the problem is divided by the input space, as in the case of this study. Model-parallelism define that several workers work on different parts of the model. Data-parallelism can also refer to SIMD instructions in some literature. To avoid confusion we will denote SIMD instructions as SIMD parallelism, however the context will also determine the semantics.

- Processing Unit A processing unit is an electronic circuitry that carry out arithmetic, logical, control and I/O operations. In this study we generally used the term processing unit incorrectly to mean hardware threads, however, in many cases the number of hardware threads equals the number of processing units, i.e. cores on the coprocessor.

- **Performance Model** A performance model is a model expressing the characteristics of a system in terms of resources consumed, resource contention, delays, etc. Its main purpose is to model a realistic system in order to provide insight of how a proposed system may behave.

- **Theoretical Analysis** A way of expressing the behaviour of an algorithm theoretically. That is, how the algorithm is expected to behave in different configurations.

## Chapter 1

### Introduction

Traditional applications are created by engineers who strictly feed the computer with instructions. Throughout the history of computers, the abstraction level have shifted from hardware-near to higher level languages eliminating details from the engineer. Nevertheless, it is still the engineer who instructs the computer what actions to take, although through a higher level of abstraction.

Deep learning algorithms learn from their own experience rather than that of the engineer. The necessity of programmers micro-managing the computer becomes less relevant, instead engineers focus on developing and implementing sophisticated deep learning models that are able to *learn* to solve complex problems.

We find these techniques intriguing, their characteristics offer a new way to think of software engineering. Therefore we decided to investigate them further, focusing on how to lower the learning time. This thesis introduces the reader to the concepts of deep learning and the Intel Xeon Phi. In the study we design, implement and evaluate a parallelization scheme applied to a CNN. Moreover, a theoretical analysis is carried out and a performance model is developed and evaluated.

This chapter is organized as follows. First deep learning and the Intel Xeon Phi are introduced. Thereafter the motivation, problem, goals and research question are discussed. Lastly, the approach is described together with the contributions and limitations of the study.

#### 1.1 Deep Learning and the Intel Xeon Phi

Machine learning is the science of making computers perform actions without explicitly programming them. By teaching computers how to perform a task they can gain experience and improve their skills in performing it [6].

Deep learning is a sub-field of machine learning which in contrast to machine learning comprises multiple layers of representations. In essence stacking of multiple layers allows deep learning algorithms to solve more complex problems than those of shallow, traditional machine learning algorithms [7]. These deep hierarchical models are inspired by the visual cortex of mammals where higher level of representations are based on lower representations [8].

A core component of deep learning, Deep Neural Networks, or DNNs, is the underlying representation model of deep learning algorithms. The first network that deserves the name deep was developed by Fukushima in 1979, which interestingly was a CNN, however, neural networks dates back even further. It was first in 1981 (Werbos et al.), the first efficient implementation of the important back-propagation algorithm was applied to

neural networks. Later, in 1989 LeCun et al. applied the techniques to CNNs and in 1998 published the famous LeNet [9].

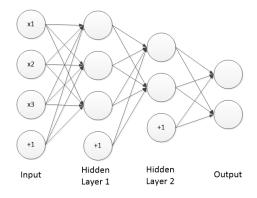

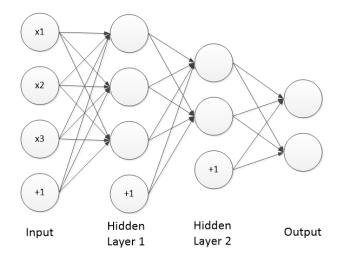

Deep Neural Networks (DNNs) can be visualized as weighted graphs as depicted in *Figure 1.1.1*. In a nutshell DNNs are able to make predictions by forward propagating an input through the network. After a forward pass through the network, the output layer contains a vector comprising the prediction. For instance, an image forwarded through the network results in a vector comprising classifications at the output layer [10].

Back-propagation is the process of learning the network. Back-propagation is a technique used in supervised learning to update the weights of the network based on the calculated loss in the forward pass. The ultimate goal of learning is to optimize the network such that the deviation between the prediction of each sample seen so far, and the desired output (label) of that sample is as low as possible [11].

In this study we focus on supervised deep learning of CNNs using the back-propagation algorithm. Supervised learning uses large labelled datasets to train the network. Each prediction is compared to the label and weight parameters are adjusted according to the errors in prediction [9].

A Convolutional Neural Network (CNN) is a variant of a DNN introducing two new layer types: *convolutional*- and *pooling-layers*. Inspired by the visual cortex of animals, CNNs are applied to state-of-the-art applications, including computer vision and speech recognition [7].

A performance model provides insight of how a system is expected to perform in terms of resources consumed and contentions. A performance model can model the intended behaviour of a system without the system at hand [12].

Theoretical analysis aims to predict the resources required by an algorithm. The results of a theoretical analysis allows to express and discuss the algorithm [13].

High Performance Computing (HPC) and larger datasets have paved the way for the success of deep learning algorithms. Although the current hype, not much work target the Intel Xeon Phi coprocessor. The Intel Xeon Phi comprises up to 61, 1.2 GHz cores, and each core can switch between 4 hardware threads in a round-robin manner. Even if each core has its own Level 2 cache, cores can share cache data internally. Therefore the coprocessor can be thought of a shared-memory, many-core coprocessor [14]. The Intel Xeon Phi used in our experiments is of type 7120p.

Figure 1.1.1: A DNN.

Deep learning have emerged from universities to industry in a rapid pace. Applications of deep learning can be found everywhere, one example of a deep learning application is the Android voice recognition [15]. Other applications include face recognition, self-driven cars, predicting liver diseases, image classification, and Skype Translate [16, 17, 18, 3, 15] - and the future will certainly yield even more.

There is, undoubtedly, a growing interest for deep learning, several large companies, including Google, Microsoft and Nvidia have announced their interest. Google acquired DeepMind in 2013 [19], a company focusing solely on deep learning. Researchers at Google also participated (and won some of the sub-challenges) in the latest ImageNet competition (2014) [20]. Microsoft perform research in the area as well. In an article published in February 2015 (this year), researchers at Microsoft claim that they outperformed a human on the 2012 version of the ImageNet dataset [21]. At a conference in March 2015 the co-founder of Nvidia, Jen-Hsun Huang, presented their new gears in conjunction with deep learning and CNNs [22]. There is no doubt deep learning is a hot topic in computer science.

Supervised learning is computational costly and time consuming - in many cases several weeks are required to complete a training session; large neural networks comprise millions, if not billions of computations. Unfortunately, large delays in training highly limit their usage in practice as many parameters often needs to be tested, and each test requires a full session of training. Intel bring High Performance Computing to consumers in form of the *Intel Xeon Phi* coprocessor. Numerous work previously target Graphical Processing Units GPUs, e.g. [23, 24], fewer target the coprocessor, leaving the potential of the *Xeon Phi* unexplored. Adopting deep learning algorithms for the *Xeon Phi* could decrease the training time from weeks to days, or from days to hours, allowing the coprocessor to be considered for supervised deep learning. Moreover, this allows consumers already invested in a *Xeon Phi* to use it for deep learning applications.

The main goal of this thesis is to investigate and position the *Intel Xeon Phi* in the context of supervised deep learning in general and CNNs in specific. To achieve this, the following sub-goals have been identified,

- Find an appropriate implementation targeting an unexplored deep learning algorithm (later narrowed down to CNNs);

- Design a parallelization scheme and adopt it to the selected implementation;

- Perform evaluation, collect data required for analysis and analyse the results;

- Perform a theoretical analysis, in a hardware independent model, to understand

and describe the algorithm. The theoretical analysis should help understand the resources required by the algorithm and what theoretical bounds that can be expected.

E.g. how much work is required to train the network and how much faster (in terms

of execution time) is the algorithm expected to perform when using multiple cores

instead of one core;

- Design and evaluate a performance model extending the theoretical model (as derived in the theoretical analysis) by including hardware characteristics. A performance model answers *what-if* questions with respect to the number of threads that goes beyond the number of hardware threads supported by the coprocessor. The performance model can also be used to predict the execution time for varying number of inputs, epochs and architectures;

This thesis will answer the research question:

**RQ1**: What is the potential of Intel Xeon Phi for supervised deep learning algorithms?

In this thesis we design a parallelization scheme, named *CHAOS*, which we adapt to be used with an existing implementation. *CHAOS* is evaluated experimentally on the MNIST [25] dataset using varying CNN architectures and thread counts. The evaluation is performed on three different platforms. We thoroughly analyse the algorithm theoretically and conclude its theoretical bounds. The theoretical model is further extended into a performance model accounting for hardware characteristics of the coprocessor. The performance model is evaluated on the coprocessor and used to predict for varying thread counts beyond that of the Intel Xeon Phi.

Our main contributions of this thesis include,

- our parallelization scheme *CHAOS* for the Intel Xeon Phi;

- experimental evaluation of the implementation using the MNIST dataset;

- development and validation of a corresponding performance model;

The scope of this study is limited to deep learning in general and CNNs in specific. For the evaluation we used one dataset (MNIST), one implementation yet several CNN architectures, platforms and thread counts. The reader should be aware of that the study is an empirical evaluation of deep learning algorithms, and do not intend to re-implement the algorithm for the coprocessor. Neither is the intention to cover all deep learning algorithms or datasets available. The project is time-boxed, time is a vital factor that cannot be neglected - training networks takes severe amount of time.

We limit ourselves to Intel Xeon Phi even though optimizations implicitly apply to other Intel architectures as well, however, no comparison will be done for GPUs (or other competing architectures). The main intentions of the theoretical model and the performance model are to discuss the algorithm and may therefore have some limitations in practice.

The thesis is intended for anyone interested in deep learning and High Performance Computing (HPC) in general. Readers searching for performance results related to deep learning and the coprocessor should especially be interested in this study as it contributes to an otherwise sparse set of work in the area. Knowledge of basic concepts in computer science are expected, an introduction to the important topics is carried out in *chapter 2*. Readers new to deep learning and/or Intel Xeon Phi can consider this thesis a nice introduction to the topics. Researchers in the area should especially find the empirical results, the parallelization scheme *CHAOS* and the performance model to be of interest. We also recognize the industry as a target group of this work as more applications use deep learning algorithms in business, and companies may already been invested in a coprocessor.

#### 1.2 Related Work

This chapter discusses previous research related to machine learning, deep learning and CNNs. Additionally, work targeting Intel Xeon Phi outside the scope of machine learning, deep learning and CNNs is also included. Overall, we find the research for the coprocessor and deep learning to be sparse, and that of GPUs to be dense.

Error rates define the number of images incorrectly predicted by the network and helps conclude the prediction accuracy of the network.

One epoch is an iteration of training, networks are trained for a set of epochs. In each iteration all inputs of the training dataset is considered once by the network.

#### 1.2.1 Datasets in Related Work

NORB [26] contains 50 toy objects in 5 categories captured in different conditions and angles. Its main intention is for 3D object recognition. CIFAR 10 [27] consists of 60,000 colour images divided into 10 classes. The MNIST [25] dataset of handwritten digits contains 60,000 training images, and 10,000 testing images. The ImageNet [20] dataset contains over 15,000,000 images divided in 22,000 categories. The number of images and categories increase by the year, earlier competitions may therefore have a smaller set of image (1.2 million and 1,000 categories in the set at 2010).

#### 1.2.2 Applications of Intel Xeon Phi

Previous work related to machine learning for the coprocessor is sparse if compared to other architectures such as GPUs. However, progress have been made for both deep- and shallow-models. Shallow models have shown to solve simple well-contained problems. However, complicated problems cause difficulties for shallow models, and many-layered (deep) models (e.g. deep neural networks) have shown more successful for the task. Whereas traditional models comprise one or two layers, deep models comprise multiple layers [7].

In this chapter we introduce previous work for Support Vector Machines (SVMs), Restricted Boltzmann Machines (RBMs), sparse auto encoders and the Brain-State-in-a-Box (BSB) model. In addition some related work outside the context of deep learning is included.

In [28], Yang You et al. present a library for parallel Support Vector Machines (SVMs), MIC-SVM, which facilitates the use of SVMs on many- and multi-core architectures including Intel Xeon Phi. Previous SVM libraries target serial execution paradigms and GPUs. One such library is the LIBSVM which is a sequential library that eases the use of SVMs for programmers [29]. Experiments performed on several known datasets showed up to 84x speed up on the Intel Xeon Phi compared to the sequential execution of LIBSVM. Their work target machine learning, our work target deep learning.

In a paper by Lei Jin et al. [30] training of sparse auto encoders and restricted Boltzmann machines were carried out on the Intel Xeon Phi. The authors managed to speed up the algorithm with a factor of 7 to 10 times compared to the Xeon CPU and more than 300 times compared to the un-optimized version executed on one thread on the coprocessor. The Xeon CPU was of type E5620 with a clock frequency of 2.4 GHz and 4 cores, and the Xeon Phi of type 5110p. The work carried out in their study target unsupervised deep learning of restricted Boltzmann machines and sparse auto encoders, our work target supervised deep learning of CNNs.

The performance gain on Intel Xeon Phi 7110p for a model called Brain-State-in-a-Box (BSB) used for text recognition is studied by Ahmed et al. in [31]. Focus lies in the recall function, i.e. the function that matches the input towards the trained patterns. According to the author, the speed up is about two-fold for the coprocessor compared to a CPU with 16 cores when parallelizing the algorithm. Their work target another architecture than ours, which target CNNs.

Studies have investigated the benefits and drawbacks in general for Intel Xeon Phi. Jianbin Fang et al. [32] investigated empirically the performance of the coprocessor. They concluded that it is possible to achieve the promised performance if the developer selects a proper parallelization strategy and puts in the hours to fully optimize the code. Existing applications will rarely utilize the coprocessor without this additional work.

In a technical report [33] carried out at Linnaeus University in the context of DNA sequencing, the authors managed to speed up their algorithm by 10x on a Intel Xeon Phi 7120p compared to a Xeon E5-2695v2 using the balanced affinity mode.

Work on the map-reduce framework for the Xeon Phi in [34] by Mian Lu et al. resulted in an optimized map-reduce framework which can be executed both for single and multiple Intel Xeon Phis. Map-reduce is a well known pattern used to distribute work over several nodes to speed up computations.

George Teodoro et al. [35] investigated the potential of large scale clusters of Intel Xeon Phis to facilitate the analysis of images retained from whole slide tissue specimens, allowing for the intense computations to be divided over several nodes. Intel Xeon Phi SE10P (5100 series) was used for the experiments.

A library to ease the burden for developer to create offloaded applications for the Xeon Phi is presented in [36] by Jiri Dokulil et al. In [37] the authors extend their work by implementing automatic tuning of algorithms to better make use of the resources of the coprocessor.

Kai-Cheung Leung et al. [38] investigated pattern matching of images on the Xeon Phi (of model 5110p) and achieved an up to 140x speed up compared to one thread on the coprocessor. The pattern matching uses k-nearest neighbours, a well-known classification method.

#### 1.2.3 Related Work Targeting CNNs

Numerous previous work target deep learning in general and CNNs in specific. We will not attempt to cover work related to deep learning in general as this scope is too wide, instead this chapter will focus on CNNs for GPUs in the context of computer vision (image classification). Work related to MNIST [25] dataset are of most interest, also NORB [26] and CIFAR 10 [27] is considered. Additionally work done in speech recognition and document processing is briefly introduced. The purpose of this chapter is to introduce the state-of-the-art in the area of GPUs and CNNs.

Work presented in [23] by Dan Cireşan et al. target a CNN implementation raising the bars for the CIFAR10 (19.51% error rate), NORB (2.53% error rate) and MNIST (0.35% error rate) datasets. The training was performed on GPUs (Nvidia GTX 480 and GTX 580) where the authors managed to decrease the training time severely - up to 60 times compared to sequential execution on a CPU - and decrease the error rates to an, at the time, state-of-the-art accuracy level.

Jordan Vrtanoski et al. [39] showed a 25.8x speed up on an ATI 5870 GPU compared to a Xeon W3530 CPU when training the model on the MNIST dataset.

Work carried out by Dan Cireşan et al. [40] performed almost human-like on the MNIST dataset, achieving a best error rate of 0.23%. To be compared to the performance of humans, about 0.20%. The authors trained the network on a GPU.

The ImageNet challenge aims to evaluate algorithms for large-scale object detection and image classification based on the ImageNet dataset. Work by Alex Krizhevsky et al. [41] entered the 2012 challenge. The authors reduced the error rate of the test set to 15.3% from the second best 26.2% using a CNN with 5 convolutional layers. For

the experiments, two GPUs (Nvidia GTX 580) were used only communicating in certain layers. The training lasted for 5 to 6 days.

In a later challenge, ILSVRC 2014, a team from Google entered the competition with GoogleNet, a 22-layer deep CNN and won the classification challenge with a 6.67% error rate. The training was carried out on CPUs. The authors state that the network could be trained on GPUs within a week, illuminating the limited amount of memory to be one of the major concerns [3].

Work by Omry Yadan et al. [24] used multiple GPUs to train CNNs on the ImageNet dataset using both data- and model-parallelism, i.e. either the input space is divided into mini-batches where each GPU train its own batch (data parallelism) or the GPUs train one sample together (model parallelism). The work does not compare to CPUs, however, using 4 GPUs (Nvidia Titan) and model- and data-parallelism, the network was trained for 4.8 days.

Inchul Song et al. [42] constructed a CNN to recognize face expressions and developed a smart-phone app in which the user can capture a picture and send it to a server hosting the network. The network, predicts a face expression and sends the result back to the user. With the help of GPUs (Nvidia Titan), the network was trained in a couple of hours on the ImageNet dataset.

Experiments carried out on the NORB [26] dataset performed by Dominik Scherer et al. [43] showed up to 115x speed up trained on an Nvidia GTX 285 compared to a CPU implementation (Core i7 940). After training the network for 360 epochs, an error rate of 8.6% was achieved.

Dan Cireşan et al. [1] combined multiple CNNs to classify German traffic signs and achieved a 99.15% recognition rate (0.85 % error rate). The training was performed using an Intel Core i7 and 4 GPUs (2 x GTX 480 and 2 x GTX 580).

Researchers have also found CNNs successful for speech tasks. Large vocabulary continuous speech recognition deals with translation of continuous speech for languages with large vocabularies. Tara N. Sainath et al. [44] investigated the advantages of CNNs performing speech recognition tasks and compared the results with previous DNN approaches. Results indicated on a 12-14% relative improvement of word error rates compared to a DNN trained on GPUs.

Kumar Chellapilla et al. [45] investigated GPUs (Nvidia Geforce 7800 Ultra) for document processing on the MNIST [25] dataset and achieved a 4.11x speed up compared to the sequential version executed on a CPU (Intel Pentium 4, 2.5 GHz).

#### 1.2.4 Example of Implementations and Libraries

This section enumerates some useful libraries and implementations found during our research study. For each library we present the name, platform, and programming language.

| Name                       | Architecture Support  | Programming Language |

|----------------------------|-----------------------|----------------------|

| Cuda-Convnet2 <sup>1</sup> | GPU                   | C++/CUDA             |

| $Tiny CNN^2$               | CPU                   | C++                  |

| Eblearn <sup>3</sup>       | CPU/GPU               | C++                  |

| $C++$ training of $CNN^4$  | CPU                   | C++                  |

| NNforge <sup>5</sup>       | CPU/GPU               | C++                  |

| $RaPyDLI^6$                | GPU/MIC <sup>11</sup> | Python/C++/Java      |

| $Caffe^7$                  | CPU/GPU               | C++                  |

| Torch <sup>8</sup>         | CPU/GPU               | C/CUDA 12            |

| Theano <sup>9</sup>        | CPU/GPU               | Python               |

| Fnnlib <sup>10</sup>       | CPU                   | C++                  |

Table 1.2.1: Some useful implementations and libraries for deep learning and CNNs.

#### 1.3 Outline

The thesis is organized as follows. In *chapter 2* the reader is introduced to the topics covered in the thesis. *Chapter 3* covers the software development and experiments followed by the results of the evaluation in *chapter 4*. *Chapter 5* performs a theoretical analysis of the algorithm. Based on the analysis, a performance model is designed and evaluated in the *section 5.4*. An analysis of both the theoretical- and experimental findings, and answer to the research question, is presented in *chapter 6*. The thesis is closed with reflections, conclusions and future work in *chapter 7*.

<sup>&</sup>lt;sup>1</sup>https://code.google.com/p/cuda-convnet/source/

<sup>&</sup>lt;sup>2</sup>https://github.com/nyanp/tiny-cnn

<sup>&</sup>lt;sup>3</sup>http://eblearn.sourceforge.net/

<sup>&</sup>lt;sup>4</sup>http://people.idsia.ch/ ciresan/

<sup>&</sup>lt;sup>5</sup>http://milakov.github.io/nnForge/

<sup>&</sup>lt;sup>6</sup>http://salsaproj.indiana.edu/RaPyDLI/

<sup>&</sup>lt;sup>7</sup>http://caffe.berkeleyvision.org/

<sup>&</sup>lt;sup>8</sup>http://torch.ch/

<sup>&</sup>lt;sup>9</sup>https://github.com/Theano/Theano/

<sup>&</sup>lt;sup>10</sup>http://sourceforge.net/projects/fnnlib/

<sup>&</sup>lt;sup>11</sup>Many Integrated Core - an architecture from Intel which combines several cores on one chip. The Intel Xeon Phi is the brand name used for Intel's MIC architecture.

<sup>&</sup>lt;sup>12</sup>CUDA is a parallel computing platform and API facilitating the use of GPUs for general purpose processing, also known as GPGPU.

## Chapter 2

## **Background**

The theory chapter introduces the core topics of the thesis including: High Performance Computing, Intel Xeon Phi, machine learning, deep learning, Deep Neural Networks (DNNs), and Convolutional Neural Networks (CNNs). Moreover, some optimization techniques for the coprocessor and parallelization schemes are discussed.

#### 2.1 Intel Xeon Phi

High Performance Computing, devices pushing the computations boundaries beyond  $10^{12}$  floating points operations per second (TFLOPS) are not only used by industry but are also made available to consumers as off-the-shelf solutions. As the increasing performance of single processing units have plateaued, more cores haven been added to the same chip to increase performance. Moreover, several nodes can be connected in a network to further increase the computational capabilities. This introduce new advantages for developers if they are able to fully make use of the hardware and deal with the demands high parallel computing entails [46].

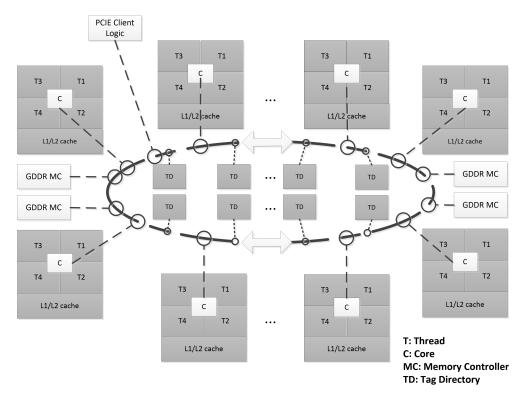

The Intel Xeon Phi used in this study is of model 7120p, and facilitates 61 cores, each with a clock frequency of 1.2 GHz. The coprocessor can achieve up to 1.2 TFLOPS performance. It facilitates 16 GB memory with a maximum theoretical bandwidth of 352 GB/s. Each core has its own private L1 (Level 1) and L2 (Level 2) cache. The L1 cache is 32KB wide for instructions and data respectively. The L2 cache combines the data and instructions into a 512KB wide space[47, 48]. Figure 2.1.1 shows an overview of the coprocessor. More details can be found in Appendix A.

Intel emphasize the simplicity of porting applications to the coprocessor: "Moving a code to Intel Xeon Phi might involve sitting down and adding a couple lines of directives that takes a few minutes. Moving a code to a GPU is a project." [14]. Even if changes to the code is required to fully make use of the coprocessors' capabilities, the fundamental thinking's of the implementation does not have to change. If written in a language supported (such as FORTRAN or C(++)) the Intel compiler will take care of the compilation for the coprocessor automatically. Additionally, time spent optimizing for the Intel Xeon Phi will result in an optimized version for the Xeon processor as well [14].

The coprocessor runs its own Linux operating system, through ssh it is possible to communicate to it from the host over the network stack. Programs can either be executed in native mode, where they execute on the device, or in offload mode, executed on the host where work is offloaded to the coprocessor [48]. The coprocessor used in our study runs a  $\mu$ OS of version 2.6.38.8 and a software stack (MPSS) of 3.1.1.

Each core can switch between 4 hardware threads, each thread can only execute every

second cycle in a round-robin fashion, and hence at least two threads need to be running for full utilization. However, in most cases even more threads can be beneficial due to memory latencies - threads not executing can perform memory fetches while waiting. To minimize memory latencies, the coprocessor automatically perform pre-fetching of data, pre-fetch commands can also be issued programmatically by the developer [47, 49].

Figure 2.1.1: The architecture of Intel Xeon Phi.

The interconnect ring (in the center of *figure 2.1.1*) is bidirectional and consist of three sub-rings. The largest ring carries data, the next second largest ring carry instructions and the smallest carry data flow commands. When a memory access occur to the L1 cache and misses, the L2 cache will be queried. If the data is not contained in the core's L2 cache, a request will be made to the Tag Directory, TD. The TD contain the memory addresses of data in L2 cache for all the cores on the MIC, hence data can be transferred between cores, over the ring, and do not need to be fetched from the main memory. If data is found in the L2 cache about 250 clock cycles of waiting is omitted and if found in the L1 cache it 20 clock cycles of wait-time is omitted - therefore data locality is essential. The compiler issues hardware pre-fetches to mitigate memory wait times for future instructions which is essential to fully make use of the vector processing unit (VPU). The vector processing unit execute SIMD (Single Instruction Multiple Data) instructions which allows for multiple operations to be carried out simultaneously on different parts of the data [49, 47].

Each cache (both L1 and L2) at each core has a Translation Lookaside Buffer (TLB) which maps virtual and physical memory addresses. It also have its own vector processing unit (VPU) which can perform 8 (8x64) double precision or 16 (16x32) single precision operations in one cycle. The level of precision depends on the number of decimal points, i.e. the accuracy of the operations. Vectorization of code, i.e. code utilizing the VPU, can highly improve the application performance. Careful consideration of vectorization, data-locality and scalability is essential to fully utilize the Intel Xeon Phi [49, 48, 47].

In contrast, the Intel Xeon E5-2695v2 has a shared high level cache based on Intel Smart Cache technology, where all cores share 30 MB of memory. This allows the cores

to dynamically share the space as needed [50].

#### 2.2 DNNs and CNNs

A short introduction to machine learning, and deep learning is carried out in this chapter. Deep neural networks (DNNs) and convolutional neural networks (CNNs) will be highlighted with the specifics required to fully understand the study - the section1 will make no attempt to cover the full aspect of deep learning.

Tom M. Mitchell provides a formal definition of machine learning algorithms in his book *Machine Learning* [51]: "A computer program is said to learn from experience E with respect to some class of tasks T and performance measure P, if its performance at tasks in T, as measured by P, improves with experience E" [51, p. 2]

A deep neural networks is the underlying model used in deep learning. Many variations of deep neural networks exist, roughly divided into three categories: supervised, unsupervised and hybrid. The categorization is based on how the network learn. An unsupervised configuration learn patterns in data without any assistance, i.e. it has no prior knowledge of the labels of the data. On the contrary, supervised learning requires large datasets of labelled data. Hybrid networks is a combination of the both. Examples of unsupervised configurations are restricted Boltzmann machines and auto encoders. Recurrent Neural Networks and CNNs are both examples of supervised. The latter is the focus of this study [7].

Deep learning and DNNs are not new concepts, perhaps the first neural network that deserve the name deep was introduced by Fukushima in 1979, and this was also a CNN. However, due to larger datasets, better computational abilities and practical achievements, deep learning have gain an increase in popularity lately. In essence they are multi-layer models constructed to learn various levels of representations where higher level representations are described based on the lower level ones [9].

The mammal visual processing system is hierarchical (deep) in nature. Higher level features are abstractions of lower level ones. E.g. to understand speech, waveforms are translated through several layers until reaching a linguistic level. A similar analogy can be drawn for images, where edges, and corners are lower level abstractions translated into more spatial patterns on higher levels. Moreover, it is also known that the animal cortex consists of both simple and complex cells firing on certain visual inputs in their receptive fields. Moreover, simple cells detect edge-like patterns whereas complex cells are locally invariant, spanning larger receptive fields. These are the very fundamental properties of the animal brain inspiring DNNs and CNNs. *Figure 2.2.1* depicts a DNN consisting of one input layer, one output layer and two hidden layers, CNNs are covered in more detail later in this chapter [7, 8].

Figure 2.2.1: A deep neural network.

#### 2.2.1 DNN Architecture

The architecture of a DNN consists of multiple layers of neurons. Neurons are connected to each other through edges (weights) (figure 2.2.1). The network can simply be thought of as a weighted graph; a directed acyclic graph represent a feed-forward network. The depth and breadth of the network differs as may the layer types. Independent of depth, a network have at least one input- and one output-layer. A neuron have a set of incoming weights attached which have corresponding outgoing edges attached to neurons in the previous layer. Also a bias term is used at each layer as an intercept term. The goal of the learning process is to adjust the network weights and find a global minimum by reducing the overall error, i.e. the deviation between the predicted and the desired outcome of all the samples. The resulting weight parameters can thereafter be used to make predictions of inputs not yet seen [52].

#### 2.2.2 Forward Propagation

Forward propagation proceeds by performing calculations at each layer until reaching the output layer. At the output layer it is common to apply a soft max function (or similar) to squash the output vector and hence derive the prediction. The output on each layer is calculated as the weighted sum of the outputs of connected neurons at the previous layer sent through an activation function. Calculating the output given the input can be done using the equation  $y_i^l = \sigma(x_i^l) + I_i^l$  where  $y_i^l$  is the output value of neuron i at layer i and i is the input value of the same neuron. The i is used for the input layer when the output i is non-existing, i.e. there is no previous layer. The input i can be calculated as i is non-existing, i.e. there is no previous layer. The input i in the current layer i and i in the previous layer, and i in the output of the ith neuron at the previous layer. To clarify: the input of a neuron i in the current layer is the weighted sum of the connected neurons i in the previous layer. In this example the i sigmoid function is used as an activation function - i another popular choice. The goal of activation functions are to return a normalized value (i sigmoid return [0,1] and i and i [-1,1]) [53, 52].

#### 2.2.3 Back-propagation

Back-propagation is the process of propagating errors, i.e. the loss calculated as the deviation between the predicted and the desired output, backward in the network, by adjusting

the weights at each layer. The stochastic gradient descent seeks to find the global minimum of the weight parameters by adjusting the weights in relation to the error (loss) of the prediction. After the forward propagation has been performed, the activations for the neurons at the output layer are known; in the concrete example of image classification, the output vector contains the prediction of the classification. Based on the predicted output, the loss as compared to the desired output can be calculated. Back-propagation begins by calculating the loss of the prediction using a loss function; examples of loss functions are mean square error and cross entropy. Partial derivatives of the output layer are computed and propagated backward in the network. Partial derivatives of a neuron are made relative to the error at the output layer, i.e. how much the neuron participated in the faulty prediction. The equation:  $\frac{\delta E}{\delta y_i^l} = \sum w_{ij}^l \frac{\delta E}{\delta x_i^{l+1}}$  denotes that the partial derivative of neu-

ron i at the current layer l is the sum of the derivatives of connected neurons at the next layer multiplied with the weights, assuming  $w^l$  denotes the weights between the maps. Consequently, weights are updated by subtracting a gradient from each weight parameter (more on this when considering CNNs below). Additionally, a decay is commonly used to control the impact of the updates, which is omitted in the above calculations. More concretely, the algorithm can be thought of as updating the weights on each layer based on "how much it was responsible for the errors in the output" [53, 11].

#### 2.2.4 Overfitting, Dropout and Early Stopping

Overfitting a network leads to good performance on the training set however bad performance on the test set, i.e. the network rather memorizes than learn features. Overfitting occur when the model have too many parameters relative to the number of samples and hence many combinations of the parameters can model the same relationship between samples. Traditionally the problem was mitigated by training several networks, and then average them or otherwise validate them against the test set before continue training. However, this process is expensive, and hence a new method called dropout was introduced in 2012 by Hinton et al. who discovered the possibility to leave out every node with a probability of 0.5 at back-propagation - a cheap way of averaging a neural network. Results show that the need to stop training earlier due to bad convergence was reduced as well [54]

#### 2.2.5 CNNs

This chapter will cover the basics of CNNs and their properties, extending the discussion in the previous section. CNNs achieve state-of-the-art performance in many applications including: speech recognition, image classification, natural language processing and machine translation [7]. The ImageNet competition push the boundaries of image recognition every year in the annual competition [20].

This section will introduce two new layer types: *convolutional layers* and *pooling layers*, and briefly discuss forward- and back-propagation.

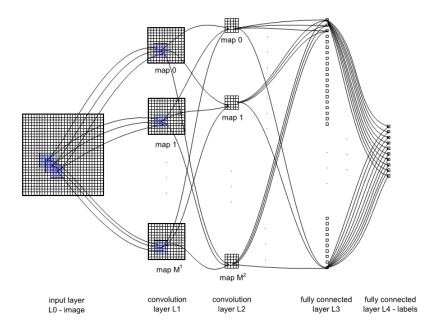

The convolutional layer consists of several feature maps where neurons in each map connects to a grid of neurons in maps in the previous layer through overlapping kernels (figure 2.2.2). The kernels are tiled to cover the whole input space. The approach is inspired by the receptive fields of the mammal visual cortex. All neurons of a map extract the same features from a map in the previous layer as they share the same set of weights. Different skipping factors can be used to determine the total amount of neurons required to scan the entire image. The convolution also removes the high density of an otherwise

Figure 2.2.2: A CNN with 5 layers emphasizing the kernels. Courtesy to Dan Cireșan et al [1].

fully connected graph, which allows for faster training since the network contains less parameters. Feature maps introduce automatic feature extraction as each feature map learns to extract features from the layer below, e.g. edges or corners (in the case of an image). *Figure 2.2.2* shows an architecture with fully connected convolutional layers, emphasizing the kernels. Feature maps differ both in size and number of neurons (map size), commonly less and larger maps are used in the lower layers and more and smaller in the top layers, which is also the case for the traditional LeNet-5 (*figure 2.2.3*) [23].

Pooling layers intervene convolutional layers and have shown to lead to faster convergence. Each neuron in a pooling layer outputs the (maximum/average) value of a partition of neurons in the previous layer, and hence only activates if the underlying grid contains the sought feature. Besides from lowering the computational load, it also enables position invariance and down samples the input by a factor relative to the kernel size [2].

CNNs are commonly constructed similar to the LeNet-5 (*figure 2.2.3*) beginning with an input layer, followed by several convolutional/pooling combinations, ending with a fully connected layer and an output layer. Recent networks are much deeper and/or wider, the GoogleNet shown in *figure 2.2.4* consists of 22 layers [2].

Forward propagation in the convolutional layer is similar to that of a fully connected layer. The input of a neuron is calculated as the weighted sum of all connected neurons over the kernel spanning the previous layer, as shown in *figure 2.2.2*. The output is the input sent through an activation function. The pooling layer is merely computing the output as the (max/average) value of a non-overlapping grid in the previous layer and map [23].

Back-propagation in convolutional layers can be divided into computing partial derivatives and computing weights. At a convolutional layer, calculations span over the set of connected maps in the previous layer. Fixating on one neuron, i, neurons in the previous layer over the kernel are updated with the derivative of i multiplied with the weight parameter connecting the two neurons. Each neuron j at the previous layer will therefore be updated several times, each time it is touched by a kernel. The resulting partial derivative

Figure 2.2.3: The traditional LeNet-5 architecture [2].

Figure 2.2.4: GoogleNet [3].

propagated to the neuron j at the previous layer can be thought of as  $\frac{\delta E}{\delta y_j^{l-1}} = \sum (w_{ji}^l \frac{\delta E}{\delta y_i^l})$  where i and j are neurons connected over the kernel. Hence, the derivative of neuron j at the previous layer is the result of each neuron i propagating its delta values to neurons it touched when performing forward propagation [23, 55].

Weights of the convolutional layers are computed by subtracting a gradient from each weight parameter. Similar to propagating the partial derivatives, the gradient is calculated based on the derivative of neuron i at the current layer multiplied with the output of neuron j at the previous layer over the kernel. A weight is updated for every kernel in a map, since weights are shared between all kernels in the same map. The goal is to minimize the error produced by the weights in the forward propagation [23, 55].

When computing partial derivatives for the pooling layer, all neurons in the layer is iterated, and the partial derivative is pushed to the derivatives of the previous layer contributing to the (max/average) value in forward propagation:  $y_{max(n)}^{l-1} = \frac{\delta E}{\delta y_n^l}$  where max(n) is the neuron providing the maximum value in forward propagation. Pooling layers do not have any weights [23, 55].

#### 2.3 Intel Xeon Phi Optimization Techniques

This chapter discusses some optimization techniques for the Intel Xeon Phi. It considers both algorithmic optimization and micro-architectural optimizations. The former targets the design of the algorithm and its data structures whereas the latter is tightly bound the underlying hardware.

#### 2.3.1 Algorithmic Optimization Techniques

The major algorithmic considerations relates to parallelism (threading, vectorization), I/O, scalability and data structures.

To fully utilize the coprocessor one should make use of both thread- and SIMD-parallelism. Thread parallelism can be achieved by using, e.g. OpenMP [56], Cilk [57] or

Thread Building Blocks[58]. SIMD parallelism make use of the wide vector processing unit (VPU) of the coprocessor [59].

A short list of features facilitating parallelism:

- *OpenMP*: A set of compiler directives, environment variables and API functions to ease shared-memory parallelism [56].

- Threading Build Blocks (TBB): Is a high performance parallel library from Intel, allowing for defining logical tasks to be performed in parallel rather than explicitly working with threads. Intel position it as a "template library for task parallelism" for C++ [58].

- Cilk (+): Intel describe the library as an extension including reducers, array notation, SIMD instructions and keywords for spawning and syncing. It is available for C and C++ [57].

- Compiler Directives: The compiler can help improve the code through directives to increase the speed and make the memory access more efficient. The default optimization level is O2 which automatically add optimizations to the code at compile time, including vectorization. The O3 level use a more aggressive loop transformation compared to O2 which may not always be beneficial [60]

- *SIMD*: AVX (Advanced Vector Extensions) instructions helps optimize the execution through efficient vectorization. SIMD can be issued through Cilk, OpenMP or as native commands for the Intel compiler [57, 56].

- *Intel Math Kernel Library*: A highly optimized math computing library supporting BLAS and LAPACK routines in C (++), FORTRAN [61].

- *Intel Integrated Performance Primitives (IPP)*: A highly optimized library for multimedia, data-processing and communication applications. The built-in functions use Intel Streaming SIMD Extensions and Advanced Vector Extensions instruction sets [62].

The compiler performs automatic vectorization if possible - in many cases it is not and the developer needs to assist the compiler vectorize the code. Using an array notation, as defined in Cilk is one option. Another is to make use of the #pragma SIMD instruction in OpenMP. The compiler will try to unroll loops if possible, the developer can enforce the compiler if necessary [56, 59].

The scalability of the application is important in order to fully utilize the cores of the coprocessor. When spawning threads it is also necessary to be aware of the overhead that comes with joining the threads at the end of the work-sharing construct. If only a small subset of the threads exit later than the majority, the execution time (span) will increase since the total time is no better than that of the worst worker. Moreover, the time to spawn and synchronize threads will be abundant. Additionally, locks to shared data also have to be reconsidered when increasing the number of threads [59].

Other scalability issues include system calls and false-sharing; *malloc* and *gettimeof-day* can be replaced by more efficient methods or omitted if possible. False-sharing occur when several threads work on data originating from the same cache line. The problem arises when threads work on data that resides nearby in memory since an update of one value forces other threads to re-fetch if working on data on the same cache lines [59].

One should try to reduce the number of memory accesses and work with data residing in the registers. For this, tiling or blocking can be used to work on cached data as far as possible [59].